- 您现在的位置:买卖IC网 > Sheet目录2001 > ISL12020MIRZ-T7A (Intersil)IC RTC/CALENDAR TEMP SNSR 20DFN

ISL12020M

27

FN6667.5

December 13, 2011

All I2C interface operations must begin with a START condition,

which is a HIGH to LOW transition of SDA while SCL is HIGH. The

ISL12020M continuously monitors the SDA and SCL lines for the

START condition and does not respond to any command until this

condition is met (see Figure 16). A START condition is ignored

during the power-up sequence.

All I2C interface operations must be terminated by a STOP

condition, which is a LOW to HIGH transition of SDA while SCL is

HIGH (see Figure 16). A STOP condition at the end of a read

operation or at the end of a write operation to memory only

places the device in its standby mode.

An acknowledge (ACK) is a software convention used to indicate

a successful data transfer. The transmitting device, either master

or slave, releases the SDA bus after transmitting eight bits.

During the ninth clock cycle, the receiver pulls the SDA line LOW

to acknowledge the reception of the eight bits of data (see Figure

17).

The ISL12020M responds with an ACK after recognition of a

START condition followed by a valid Identification Byte, and once

again, after successful receipt of an Address Byte. The

ISL12020M also responds with an ACK after receiving a Data

Byte of a write operation. The master must respond with an ACK

after receiving a Data Byte of a read operation.

Device Addressing

Following a start condition, the master must output a Slave Address

Byte. The 7 MSBs are the device identifiers. These bits are

“1101111” for the RTC registers and “1010111” for the User SRAM.

The last bit of the Slave Address Byte defines a read or write

operation to be performed. When this R/W bit is a “1”, a read

operation is selected. A “0” selects a write operation (refer to

Figure 19).

After loading the entire Slave Address Byte from the SDA bus, the

ISL12020M compares the device identifier and device select bits

with “1101111” or “1010111”. Upon a correct compare, the device

outputs an acknowledge on the SDA line.

Following the Slave Byte is a one byte word address. The word

address is either supplied by the master device or obtained from an

internal counter. On power-up, the internal address counter is set to

address 00h, so a current address read starts at address 00h. When

required, as part of a random read, the master must supply the 1

Word Address Bytes, as shown in Figure 20.

In a random read operation, the slave byte in the “dummy write”

portion must match the slave byte in the “read” section. For a

random read of the Control/Status Registers, the slave byte must be

“1101111x” in both places.

Write Operation

A Write operation requires a START condition, followed by a valid

Identification Byte, a valid Address Byte, a Data Byte, and a STOP

condition. After each of the three bytes, the ISL12020M

responds with an ACK. At this time, the I2C interface enters a

standby state.

Read Operation

A Read operation consists of a three byte instruction, followed by

one or more Data Bytes (see Figure 20). The master initiates the

operation issuing the following sequence: a START, the

Identification byte with the R/W bit set to “0”, an Address Byte, a

second START, and a second Identification byte with the R/W bit

set to “1”. After each of the three bytes, the ISL12020M responds

with an ACK. Then the ISL12020M transmits Data Bytes as long as

the master responds with an ACK during the SCL cycle following

the eighth bit of each byte. The master terminates the read

operation (issuing a STOP condition) following the last bit of the

last Data Byte (see Figure 20).

The Data Bytes are from the memory location indicated by an

internal pointer. This pointer’s initial value is determined by the

Address Byte in the Read operation instruction, and increments

by one during transmission of each Data Byte. After reaching the

memory location 2Fh, the pointer “rolls over” to 00h, and the

device continues to output data for each ACK received.

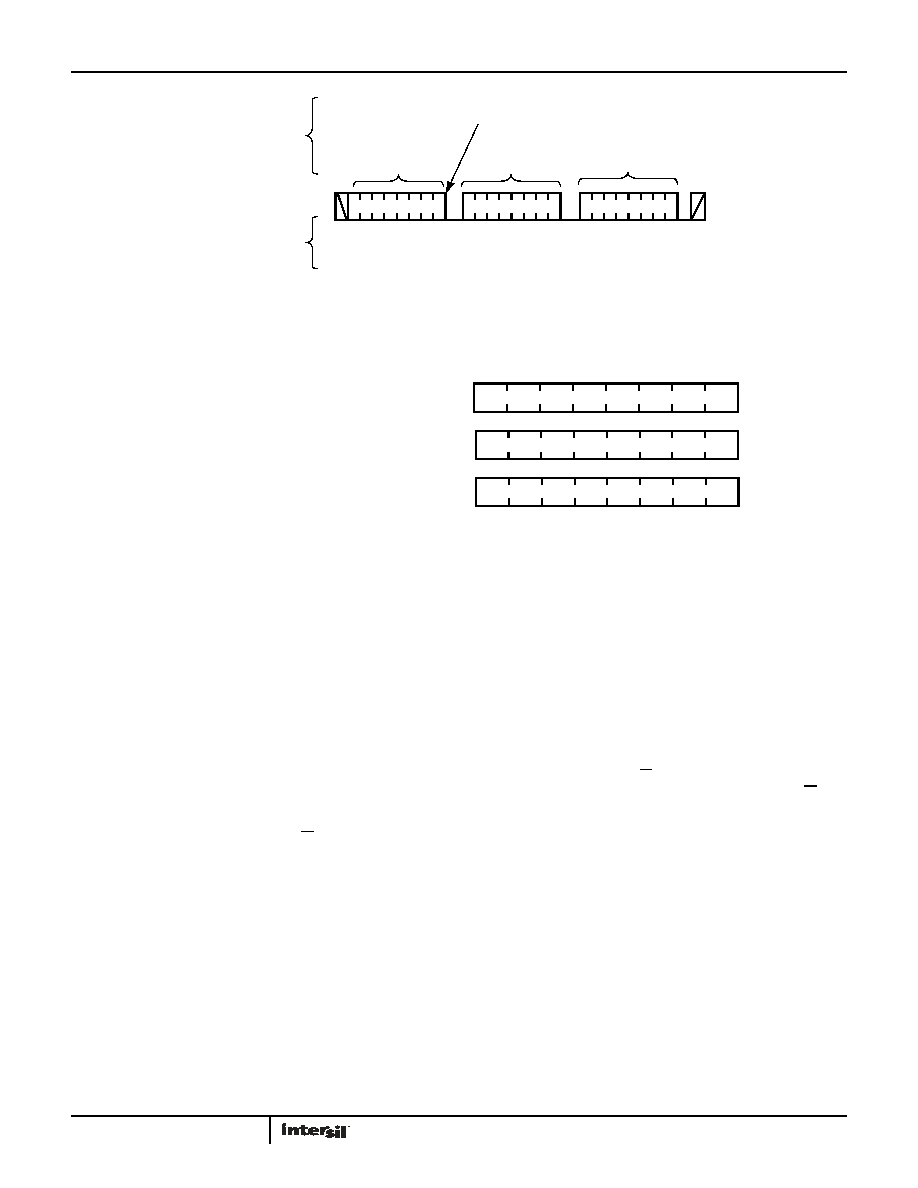

FIGURE 18. BYTE WRITE SEQUENCE (SLAVE ADDRESS FOR CSR SHOWN)

S

T

A

R

T

S

T

O

P

IDENTIFICATION

BYTE

DATA

BYTE

A

C

K

SIGNALS FROM

THE MASTER

SIGNALS FROM

THE ISL12020M

A

C

K

10

0

11

A

C

K

WRITE

SIGNAL AT SDA

00 00

11 1

ADDRESS

BYTE

FIGURE 19. SLAVE ADDRESS, WORD ADDRESS, AND DATA BYTES

SLAVE

ADDRESS BYTE

D7

D6

D5

D2

D4

D3

D1

D0

A0

A7

A2

A4

A3

A1

DATA BYTE

A6

A5

1

10

1

R/

1

WORD

ADDRESS

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISL12022IBZ-T7A

IC RTC/CALENDAR TEMP SNSR 8SOIC

ISL12022MAIBZ

IC RTC/CALENDAR TEMP SNSR 20SOIC

ISL12022MIBZ-T7A

IC RTC/CALENDAR TEMP SNSR 20SOIC

ISL12022MIBZR5421

IC RTC/CALENDAR TEMP SNSR 20SOIC

ISL12023IVZ

IC RTC/CLDR TEMP SNSR 14-TSSOP

ISL12024IRTCZ

IC RTC/CALENDER 64BIT 8-TDFN

ISL12024IVZ

IC RTC/CALENDAR EEPROM 8-TSSOP

ISL12025IVZ

IC RTC/CALENDAR EEPROM 8-TSSOP

相关代理商/技术参数

ISL12021

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock with On Chip Temp Compensation 【5ppm

ISL12021CVZ

功能描述:IC RTC LP BATT BACK SRAM 14TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 实时时钟 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 类型:时钟/日历 特点:警报器,闰年,SRAM 存储容量:- 时间格式:HH:MM:SS(12/24 小时) 数据格式:YY-MM-DD-dd 接口:SPI 电源电压:2 V ~ 5.5 V 电压 - 电源,电池:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-WDFN 裸露焊盘 供应商设备封装:8-TDFN EP 包装:管件

ISL12021IVZ

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock with On Chip Temp Compensation 【5ppm

ISL12022

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock with On Chip ±5ppm Temp Compensation

ISL12022IBZ

功能描述:实时时钟 REAL TIME CLK/CLNDR W/TEMP COMP 8 L RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12022IBZ-T

功能描述:实时时钟 REAL TIME CLK/CLNDR W/TEMP COMP 8 L RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12022IBZ-T7A

功能描述:实时时钟 REAL TIME CLK/CLNDR W/TEMP COMP 8 L RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12022M

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Power RTC with Battery Backed SRAM, Integrated ±5ppm Temperature Compensation, and Auto Daylight Saving